厚外延生长铝镓氮 (AlGaN) 替代氮化硅 (SiN) 钝化层可以消除分级极化FET 中的稳定性。

用 AlGaN 替代 SiN 钝化层可以减少来自极化 FET 中表面态的不稳定性。

来自俄亥俄州立大学和 Qorvo 公司的工程师改善了分级极化FET (polarisation-graded FET) 的设计,此类 FET 是一种适用于 5G 毫米波基站,很有前途的功率放大器。不稳定性源于界面陷阱,为了消除界面陷阱,使用厚的 AlGaN 外延层 替代 SiN 钝化层。

该小组的发言人,来自俄亥俄州立大学的 Shahadat Sohel 说,他们是首个在高功率、高线性度 AlGaN 沟道晶体管中实现 DC-RF 稳定运行(在极高的静态偏置电压条件下)的研究团队。“DC-RF 不稳定是任何晶体管中造成输出功率偏低的主要原因之一。”

分级极化FET 是富有吸引力的 GaN HEMT 替代方案(后者是高频基站领域中的领先技术),因为其具有更平坦的跨导曲线 (transconductance profile),可以实现更好的线性度。

具备这个优越性,源于纳入了一种通过对沟道中的铝组分进行线性变化而形成的三维电子气体。采用三维电子气后,偏置电压的变化对载流子体积密度的影响将微乎其微,而反过来,栅极电压的变化仅在电子饱和速度中产生微小的变化,从而实现了更佳的线性。

Sohel 和同事们并不是分级极化FET 的发明者。“但是,我们优化并改进了设计,以实现针了对 X 波段应用的创记录的线性性能。”

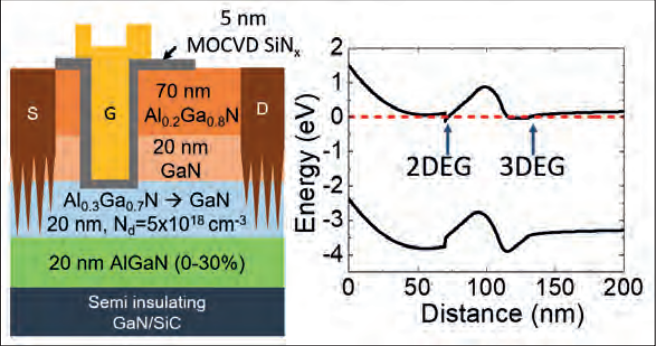

该研究小组的 FET 制备流程是:首先将 SiC 衬底装入 MOCVD 反应室,然后外延一层 GaN 缓冲层,然后是一个包含铝(铝含量在 0% 至 30% 的范围内线性变化)的 20 nm 厚 AlGaN 沟道;以及一个由组分为 Al0.3Ga0.7N 至 GaN 的20 nm 线性变化势垒构成的外延钝化区、一个 20 nm 厚 GaN 层和一个 80 nm 厚 Al0.2Ga0.8N 层。在该异质结构的内部有一种二维电子气体,它位于 GaN 和 Al0.2Ga0.8N 之间的界面上,屏蔽了表面的沟道,以确保通路区域(access region)的夹断电压比栅极区的更负。

源极和漏极电极的形成方法是:对盖层进行蚀刻、运用电子束蒸发工艺沉积 Ti/Al/Ni/Au 多层金属、并使用 850 °C 快速热退火将其转变成一种合金。栅极是采用氯气蚀刻一个 0.7 μm 宽的凹槽,然后使用 MOCVD沉积一层 5 nm 厚的 SiN 薄膜。它充当栅介电层,因而减少了栅极漏电,并且还将栅极与二维电子气隔离开。为了完成肖特基栅的制作,工程师增添了一个 Ni-Au-Ni 多层金属。

为创建一个场板,Sohel 和同事们采取了将栅极向漏极延伸 0.3 μm 的做法。这通过减弱峰值电场以及增加击穿电压,使不稳定得到了进一步的减少。

电学特性分析显示了 500 mA mm-1 的最大输出电流、具有160 mS mm-1 最大平坦跨导、和 110 V 的三端击穿电压(当栅极与漏极之间的间隔为 3.5 μm 时)。对漏电流来源所做的分析表明,肖特基栅是导致击穿的主要原因。

测量条件包括具有 0.1% 占空比、 5 μs 脉冲、5 V 的栅极静态夹断偏置电压、和高达 50 V 的漏极静态偏置电压,结果显示:对于电流崩塌和 knee-walkout(这是膝电压的增加)两种情况,不稳定性均极小。相比之下,Sohel 和同事们在 2018 年报道的采用 SiN 钝化的分级极化FET 则具有 25% 的电流崩塌和 8 V 的膝电压增加(对于 30 V 的漏极静态偏置条件)。

目前,Sohel 和同事们正在开发一种位于场板下面的牺牲层,以减小寄生电容。“我们还在就栅长和源-漏极间隔的调整开展研究,旨在提高晶体管的工作频率。”

S. Sohel et al. Appl. Phys. Express 13 036502(2020)